中規模集成電路功能測試儀的創新設計與實現

集成電路是現代電子系統的核心,其性能與可靠性直接決定了整個設備的質量。隨著半導體技術的飛速發展,中規模集成電路(MSI)因其在復雜度、成本與性能間的良好平衡,在通信、控制、消費電子等領域得到廣泛應用。MSI的功能測試是確保其出廠質量的關鍵環節,傳統測試方法效率低、精度差,難以滿足批量生產的需求。因此,設計一款高效、精準、自動化的中規模集成電路功能測試儀,對提升測試效率、降低生產成本、保障產品質量具有重要的工程價值與市場意義。

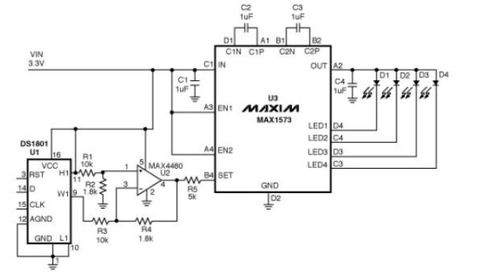

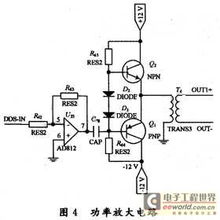

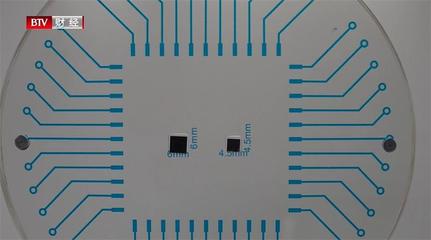

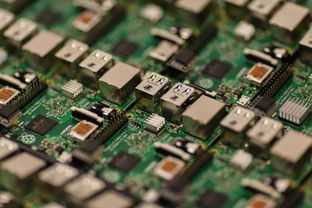

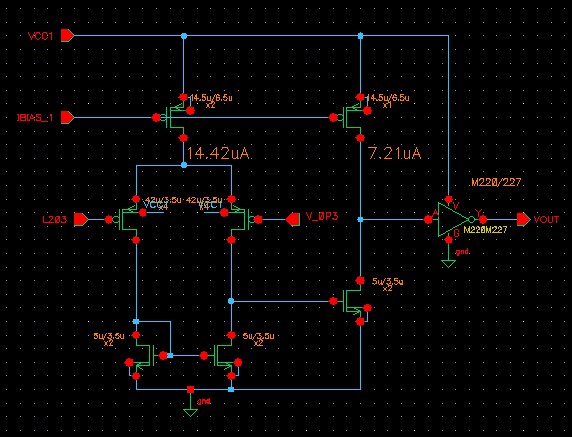

本文提出的中規模集成電路功能測試儀設計,以模塊化、智能化、高精度為核心思想,構建了一個完整的軟硬件協同測試系統。硬件平臺采用主控模塊、信號發生與采集模塊、程控電源模塊、適配接口模塊及人機交互模塊的架構。主控模塊通常選用高性能嵌入式處理器(如ARM Cortex-A系列)或FPGA,負責測試流程控制、數據處理與通信協調。信號發生模塊基于直接數字頻率合成(DDS)技術,可產生高精度、高穩定度的數字與模擬激勵信號;信號采集模塊則通過高速高精度ADC,實時捕獲被測集成電路的輸出響應。程控電源模塊提供多路可編程電壓與電流,確保被測芯片在標準工作條件下運行。適配接口模塊通過可更換的測試夾具(如零插拔力插座)和通用接口板,靈活適配不同封裝與引腳定義的MSI芯片。人機交互模塊包括觸摸屏、按鍵與狀態指示燈,提供直觀的操作界面與實時測試狀態顯示。

軟件系統是測試儀的靈魂,采用分層設計,包括底層驅動、測試內核與上層應用。底層驅動負責硬件資源的直接控制與訪問;測試內核則實現了核心的測試算法與邏輯,如測試向量生成、時序控制、響應比較與故障診斷。測試向量可根據被測芯片的功能表或真值表,通過算法自動生成,并支持手動編輯與導入。時序控制精確管理激勵施加與響應采樣的時間關系,確保建立時間與保持時間滿足要求。響應比較模塊將采集到的輸出與預期值進行比對,并記錄差異。故障診斷算法可對失效引腳或功能模塊進行初步定位,輔助分析失效原因。上層應用軟件提供圖形化測試項目編輯、參數配置、測試執行控制、數據報表生成與歷史數據管理等功能,極大提升了測試的便捷性與可追溯性。

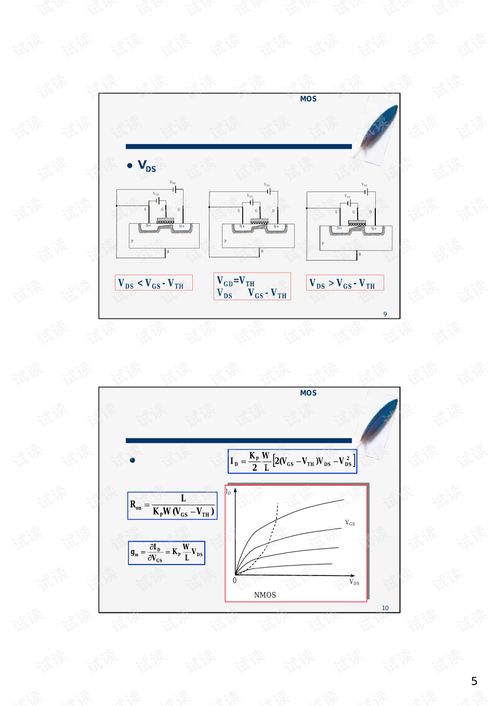

在集成電路設計層面,本測試儀的設計充分考慮了與被測MSI芯片的協同。測試儀的信號完整性設計至關重要,需通過嚴格的阻抗匹配、去耦電容布局、地平面分割與屏蔽措施,最小化信號反射、串擾與噪聲,確保測試信號的純凈度與時序準確性。測試儀的時序設計必須兼容多種MSI芯片的時序要求,如組合邏輯電路的傳輸延遲、時序邏輯電路的建立/保持時間、時鐘頻率等。通過可編程延遲線與時鐘管理單元,實現納秒級精度的時序調整。針對不同的集成電路工藝與電源電壓(如TTL、CMOS),測試儀的I/O電平需可編程適配,避免電平不匹配造成的損壞或誤判。

系統的測試流程高度自動化:用戶放置芯片并選擇測試方案后,系統自動完成上電、施加激勵、采集響應、分析判斷并輸出結果(合格/不合格及詳細參數)。測試報告可詳細記錄每項測試的通過情況、關鍵參數測量值(如輸出電壓、電流、延遲時間)以及失效日志,支持導出為CSV或PDF格式,便于質量分析與歸檔。

本中規模集成電路功能測試儀的設計,通過創新的硬件架構與智能化軟件系統的結合,實現了對各類MSI芯片功能的高效、精準、自動化測試。它不僅顯著提升了生產測試環節的效率和可靠性,降低了人力成本,其模塊化與可擴展的設計理念也使其能夠適應未來集成電路技術的發展和測試需求的演變,為集成電路設計與制造行業的品質管控提供了強有力的工具支持。未來的優化方向可包括集成更先進的邊界掃描(JTAG)測試功能、支持系統級芯片(SoC)中IP核的測試、以及引入人工智能算法進行自適應測試與預測性維護,進一步提升測試儀的智能化水平與應用范圍。

如若轉載,請注明出處:http://www.howtopass.cn/product/11.html

更新時間:2026-03-09 14:58:10