一種面向集成電路設(shè)計(jì)的數(shù)字集成電路測試系統(tǒng)設(shè)計(jì)

隨著半導(dǎo)體工藝的不斷進(jìn)步和集成電路設(shè)計(jì)復(fù)雜度的日益提升,數(shù)字集成電路(Digital Integrated Circuit, DIC)的功能驗(yàn)證與性能測試已成為保障芯片質(zhì)量、縮短產(chǎn)品上市周期的關(guān)鍵環(huán)節(jié)。傳統(tǒng)的測試方法在應(yīng)對(duì)超大規(guī)模、高速、低功耗設(shè)計(jì)時(shí)面臨諸多挑戰(zhàn)。因此,設(shè)計(jì)一種高效、精準(zhǔn)、可擴(kuò)展的數(shù)字集成電路測試系統(tǒng),對(duì)于集成電路設(shè)計(jì)流程至關(guān)重要。本文將探討一種面向集成電路設(shè)計(jì)的數(shù)字集成電路測試系統(tǒng)的整體架構(gòu)與核心設(shè)計(jì)考量。

一、 系統(tǒng)總體架構(gòu)設(shè)計(jì)

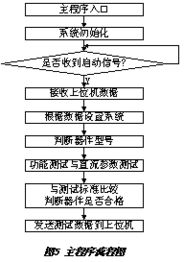

該測試系統(tǒng)采用模塊化、層次化的設(shè)計(jì)思想,旨在覆蓋從設(shè)計(jì)驗(yàn)證到生產(chǎn)測試的全流程。總體架構(gòu)可分為四大核心模塊:

- 測試向量生成與優(yōu)化模塊:此模塊是系統(tǒng)的“大腦”。它接收來自設(shè)計(jì)階段的設(shè)計(jì)文件(如網(wǎng)表、RTL代碼)和測試規(guī)格。基于故障模型(如固定型故障、路徑延時(shí)故障),利用自動(dòng)測試向量生成(ATPG)算法或形式化驗(yàn)證方法,生成高故障覆蓋率的測試向量集。集成測試壓縮技術(shù),以減少測試數(shù)據(jù)量,從而降低測試時(shí)間與存儲(chǔ)成本。

- 測試執(zhí)行與控制模塊:這是系統(tǒng)的“執(zhí)行機(jī)構(gòu)”。通常以可編程測試儀或基于FPGA的硬件平臺(tái)為核心。該模塊負(fù)責(zé)將生成的測試向量按照精確的時(shí)序施加到被測電路(DUT)的輸入端口,并同步捕獲DUT的輸出響應(yīng)。它需要具備高精度的時(shí)鐘管理、可編程的電壓/電流驅(qū)動(dòng)與測量能力,以及對(duì)各種通信協(xié)議(如JTAG、I2C、SPI)的支持,以滿足不同設(shè)計(jì)的接口需求。

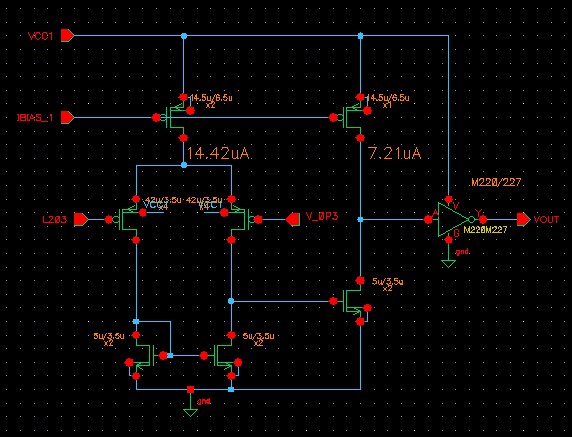

- 響應(yīng)分析與故障診斷模塊:此模塊是系統(tǒng)的“診斷中心”。它將捕獲到的輸出響應(yīng)與預(yù)期結(jié)果(黃金響應(yīng))進(jìn)行比較,判斷電路功能正確與否。更重要的是,當(dāng)測試失敗時(shí),該模塊需具備故障診斷與定位能力。通過分析失效模式,結(jié)合掃描鏈和內(nèi)置自測試(BIST)結(jié)構(gòu)信息,能夠?qū)⒐收隙ㄎ坏骄唧w的邏輯門或互連線上,為設(shè)計(jì)工程師提供快速調(diào)試的依據(jù)。

- 系統(tǒng)管理與數(shù)據(jù)交互模塊:作為系統(tǒng)的“指揮中心”,該模塊提供圖形化用戶界面(GUI)或腳本接口,供測試工程師配置測試流程、監(jiān)控測試狀態(tài)、查看測試報(bào)告。它管理與設(shè)計(jì)環(huán)境(如EDA工具)的數(shù)據(jù)交換,實(shí)現(xiàn)測試程序與設(shè)計(jì)數(shù)據(jù)的無縫對(duì)接,并負(fù)責(zé)測試結(jié)果的數(shù)據(jù)庫存儲(chǔ)與統(tǒng)計(jì)分析。

二、 面向集成電路設(shè)計(jì)的關(guān)鍵設(shè)計(jì)考量

在集成電路設(shè)計(jì)語境下,測試系統(tǒng)的設(shè)計(jì)必須與前端設(shè)計(jì)流程深度融合,即遵循可測試性設(shè)計(jì)(DFT)原則。

- DFT集成與協(xié)同:系統(tǒng)設(shè)計(jì)之初就需考慮對(duì)主流DFT技術(shù)的全面支持,包括掃描設(shè)計(jì)(Scan Design)、內(nèi)建自測試(BIST)、邊界掃描(Boundary Scan)等。測試向量生成模塊應(yīng)能直接利用設(shè)計(jì)中插入的掃描鏈結(jié)構(gòu),實(shí)現(xiàn)高效率的測試。測試系統(tǒng)與EDA工具的緊密集成,允許在設(shè)計(jì)階段就評(píng)估測試覆蓋率,并迭代優(yōu)化測試策略。

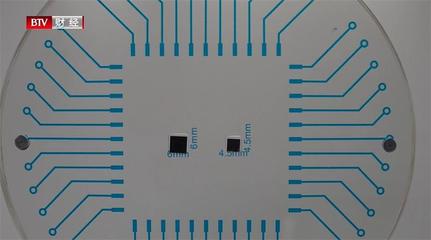

- 支持仿真與原型驗(yàn)證:理想的測試系統(tǒng)應(yīng)能無縫對(duì)接設(shè)計(jì)仿真環(huán)境。在流片前,可以利用生成的測試向量對(duì)RTL級(jí)或門級(jí)網(wǎng)表進(jìn)行軟件仿真,提前驗(yàn)證測試向量的有效性。結(jié)合FPGA原型驗(yàn)證平臺(tái),可以在真實(shí)硬件環(huán)境下進(jìn)行更接近硅片行為的系統(tǒng)級(jí)驗(yàn)證與測試,降低流片風(fēng)險(xiǎn)。

- 應(yīng)對(duì)先進(jìn)工藝挑戰(zhàn):針對(duì)深亞微米及以下工藝帶來的低功耗設(shè)計(jì)、小延遲缺陷、串?dāng)_噪聲等問題,測試系統(tǒng)需要集成相應(yīng)的測試能力。例如,支持測試功耗管理、小延遲缺陷測試向量生成、以及基于抖動(dòng)和噪聲分析的測試方法。

- 可擴(kuò)展性與靈活性:隨著芯片設(shè)計(jì)向多核、異構(gòu)、Chiplet等方向發(fā)展,測試系統(tǒng)需要具備良好的可擴(kuò)展性,能夠支持多站點(diǎn)并行測試、不同電源域管理以及復(fù)雜的互連協(xié)議測試。其硬件平臺(tái)和軟件架構(gòu)應(yīng)模塊化,便于升級(jí)以適應(yīng)新的測試標(biāo)準(zhǔn)和接口協(xié)議。

- 數(shù)據(jù)分析與智能優(yōu)化:利用大數(shù)據(jù)和機(jī)器學(xué)習(xí)技術(shù),對(duì)海量測試數(shù)據(jù)進(jìn)行分析,挖掘測試模式與缺陷分布之間的關(guān)聯(lián),可以優(yōu)化測試向量集,實(shí)現(xiàn)自適應(yīng)測試,進(jìn)一步提高測試效率與缺陷檢出率。

三、

一種面向集成電路設(shè)計(jì)的數(shù)字集成電路測試系統(tǒng),絕非簡單的硬件儀器堆砌,而是一個(gè)軟硬件深度協(xié)同、與設(shè)計(jì)流程緊密結(jié)合的復(fù)雜工程系統(tǒng)。其核心價(jià)值在于,通過在設(shè)計(jì)階段就引入高效的測試策略和可測試性設(shè)計(jì),構(gòu)建起從設(shè)計(jì)到測試的閉環(huán)反饋,從而在芯片生命周期的早期發(fā)現(xiàn)并解決問題,最終實(shí)現(xiàn)高質(zhì)量、高可靠、快速上市的數(shù)字集成電路產(chǎn)品。隨著人工智能和云技術(shù)的融入,測試系統(tǒng)將朝著更加智能化、平臺(tái)化的方向發(fā)展,為集成電路設(shè)計(jì)產(chǎn)業(yè)提供更強(qiáng)大的支撐。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.howtopass.cn/product/12.html

更新時(shí)間:2026-03-09 05:59:11