CMOS集成電路設計(二) 接口電路詳解

在CMOS集成電路設計中,接口電路是連接芯片內部核心邏輯與外部世界的關鍵橋梁。它的性能直接影響著整個系統的可靠性、速度、功耗以及抗干擾能力。本文作為CMOS集成電路設計系列的第二部分,將深入解析幾種核心的接口電路。

一、輸入接口電路

輸入接口電路的主要任務是將來自外部(如其他芯片、傳感器或開關)的信號,轉換成芯片內部CMOS邏輯能夠安全、可靠識別的電壓電平。

- 施密特觸發器輸入緩沖器:這是最常用的輸入接口之一。其核心特點是具有滯回特性,即高、低電平的翻轉閾值不同。這能有效抑制輸入信號上的噪聲和振鈴現象,提供干凈的信號給內部電路,特別適用于處理緩慢變化或噪聲較大的信號,如按鍵輸入。

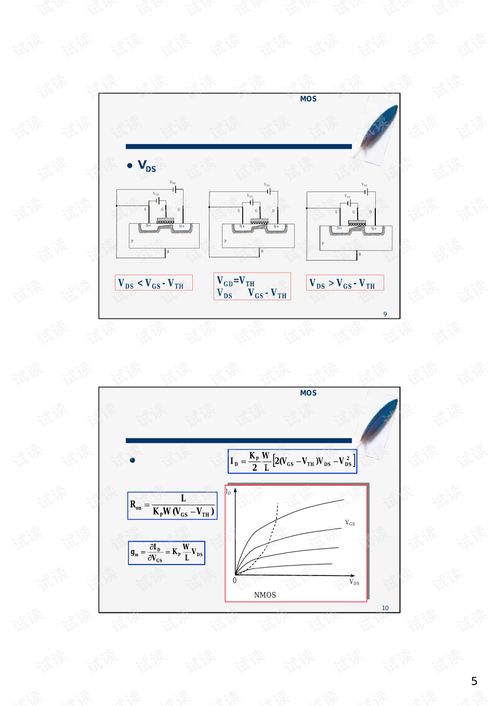

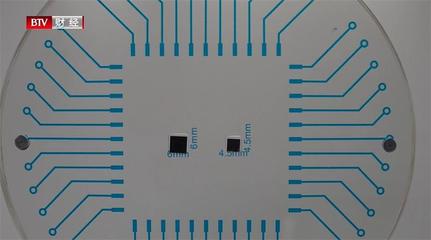

- 電平轉換輸入緩沖器:當芯片需要與不同供電電壓的器件通信時(例如,內核1.2V供電,但需要接收3.3V的輸入信號),就需要電平轉換電路。它通常采用特殊的晶體管結構或級聯方式,確保高電壓信號能被安全地轉換為內部低電壓電平,同時避免柵氧過壓損壞。

二、輸出接口電路

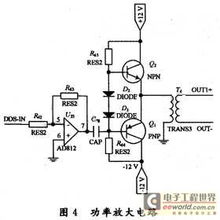

輸出接口電路負責將芯片內部微弱的邏輯信號,驅動到能夠滿足外部負載(如PCB走線、其他芯片的輸入電容)要求的電流和電壓水平。

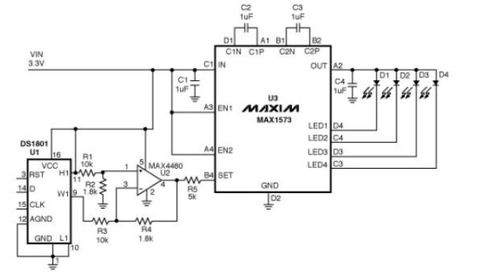

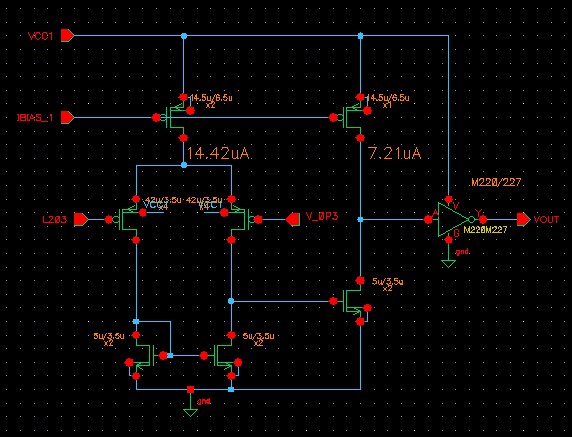

- 推挽輸出驅動器:這是最標準的CMOS輸出級,由一個PMOS上拉管和一個NMOS下拉管串聯構成。它能夠提供完整的軌到軌(從VDD到GND)電壓擺幅,并且通過調整晶體管的寬長比(W/L),可以設計出從輕負載到重負載(如驅動LED、繼電器)的各種驅動能力。設計時需要仔細權衡驅動能力、開關速度、功耗和面積。

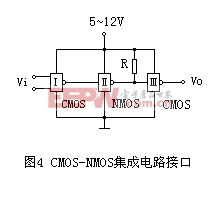

- 開漏輸出:這種輸出結構只有NMOS下拉管,沒有內部上拉。輸出端需要通過外部上拉電阻連接到電源。其最大優勢是可以實現“線與”功能,即多個開漏輸出可以直接連接在一起,只要有一個輸出為低,總線即為低。這在I2C等總線協議中被廣泛使用。它也便于實現不同電壓域之間的電平轉換。

三、雙向接口(I/O)電路

在現代芯片中,許多引腳被設計為既可以作為輸入也可以作為輸出,即雙向I/O端口。其核心是一個三態控制邏輯。

- 當設置為輸出模式時,使能輸出驅動器,內部邏輯信號被推送到引腳。

- 當設置為輸入模式時,輸出驅動器被置于高阻態(關閉),引腳上的信號通過輸入緩沖器傳入內部。

設計雙向I/O時,必須避免輸出使能和輸入信號沖突導致的“總線競爭”和過大短路電流,同時需要處理好信號方向切換時的時序問題。

四、特殊接口電路

- 靜電放電保護電路:所有與外部連接的引腳都必須集成ESD保護結構,通常采用二極管、柵接地NMOS或硅控整流器等方式,將人體模型或機器模型放電產生的高壓大電流泄放到電源或地,保護內部脆弱的柵氧。

- 差分信號接口:對于高速或高抗噪聲要求的傳輸(如LVDS、USB),常采用差分對作為接口。它使用兩根線傳輸相位相反的信號,接收端檢測兩者的電壓差。這種結構對共模噪聲有極強的抑制能力,并能以更低的電壓擺幅實現高速數據傳輸,從而降低功耗和EMI。

接口電路設計是CMOS集成電路設計中工程性與藝術性并重的環節。設計師需要在速度、功耗、面積、魯棒性和兼容性之間取得最佳平衡。理解并熟練掌握各種接口電路的工作原理與設計要點,是確保芯片在復雜系統中穩定工作的基石。隨著工藝演進和系統需求的變化,新型的接口電路技術(如基于SerDes的高速串行接口)也在不斷發展,持續學習是設計者的必備素養。

如若轉載,請注明出處:http://www.howtopass.cn/product/16.html

更新時間:2026-03-09 23:36:13